VNCHIP

Design for Testing

We provide:

Testability Design

Result Analysis and Summary

System Level Testing

Previous

Next

Design for Testing

Testability and Manufacturability

VNCHIP systematically employs structured and automated testing, refining DFT plans and enhancing fault coverage. This approach identifies blind spots and design flaws early, ensuring products meet the highest standards in mass production.

PKG

UBI

Mark

VMI

CP

FTH

FTC

SLT

FG

- Die Temp. @25°C

- Fault Coverage Test

- MFG ID

- Die Temp. @90°C

- Fault Coverage Test

- FTH_minV

- Max Power

- Guard Band(GB)

- PLL Calibration

- Speed Binning

- Per Part Database

- Die Temp. @5°C

- Fault Coverage Test

- FTC_minV

- Parallax Offset

- P/F@FTH_minV + GB

- Efuse

- Product ID

- Per Part Database

CP

PKG

FTH

UBI

FTC

Mark

SLT

VMI

FG

- Die Temp. @25°C

- Fault Coverage Test

- MFG ID

- Die Temp. @90°C

- Fault Coverage Test

- FTH_minV

- Max Power

- Guard Band(GB)

- PLL Calibration

- Speed Binning

- Per Part Database

- Die Temp. @5°C

- Fault Coverage Test

- FTC_minV

- Parallax Offset

- P/F@FTH_minV + GB

- Efuse

- Product ID

- Per Part Database

We provide:

- DFT test plan of logic ATPG & logic/memory BIST

- Stuck-at, functional, and speed fault coverage report

- Correlation analysis and report for coverage enhancement

- CP/FT Wafer test program development

- Probe card, load board, and active thermal control design

Design for Testing

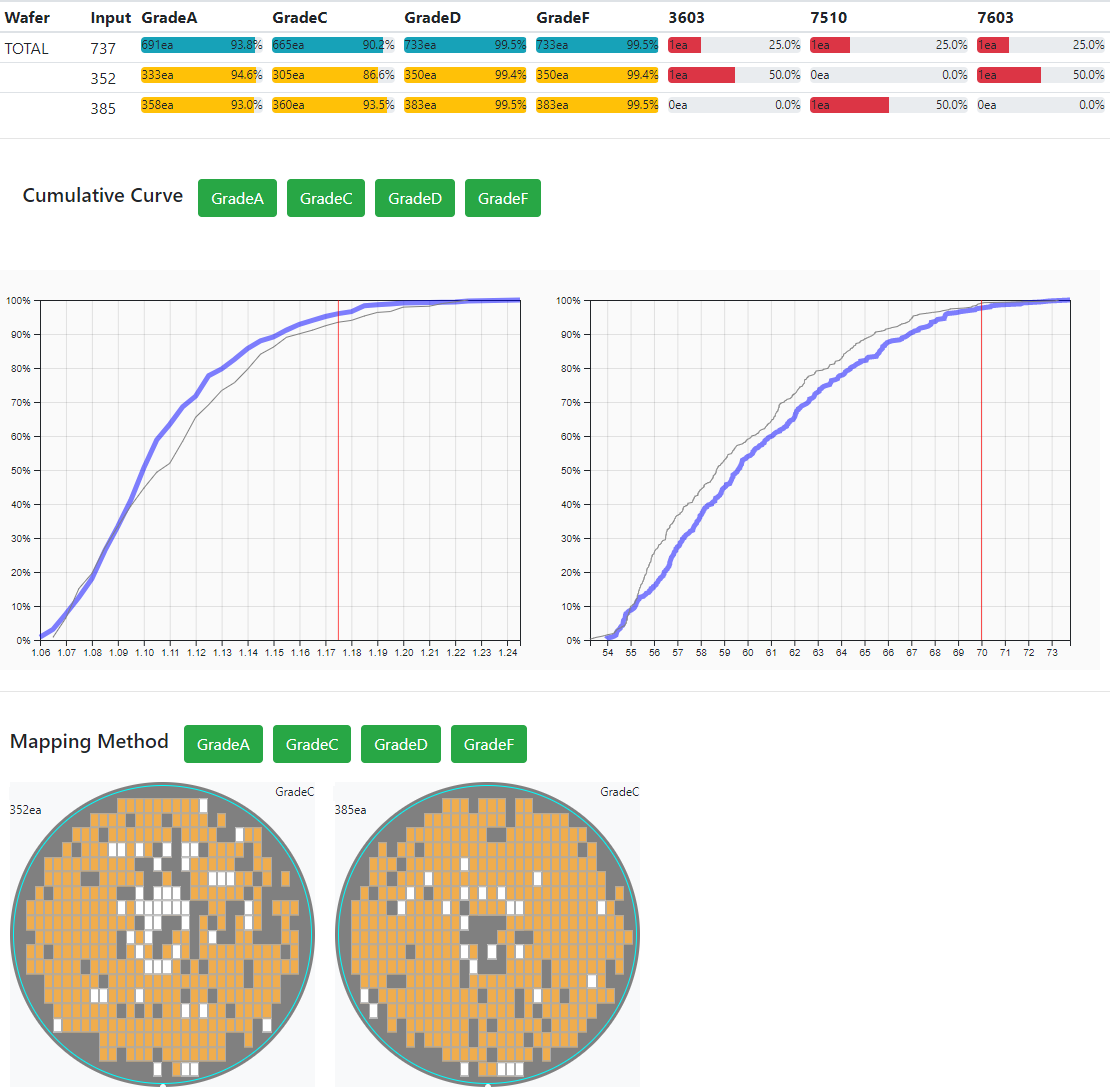

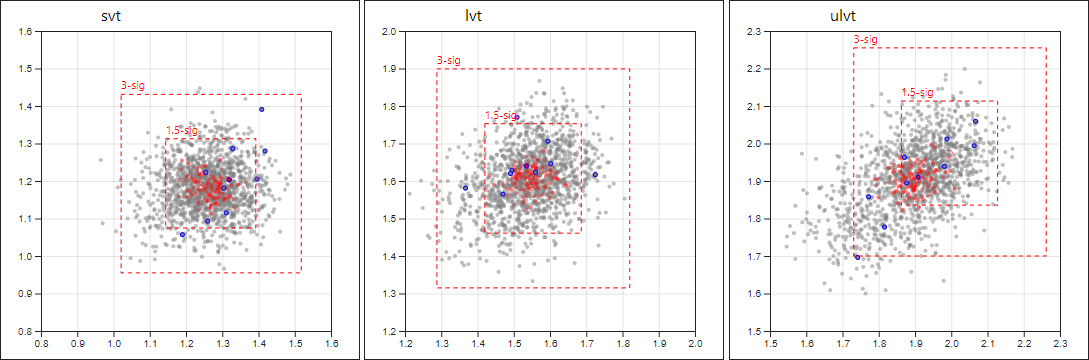

Test Result Analysis

VNCHIP uses cutting-edge DFT technology to capture and analyze chip test data, finding opportunities for design improvement. This boosts yield, cuts costs, and ensures top quality.

Design for Testing

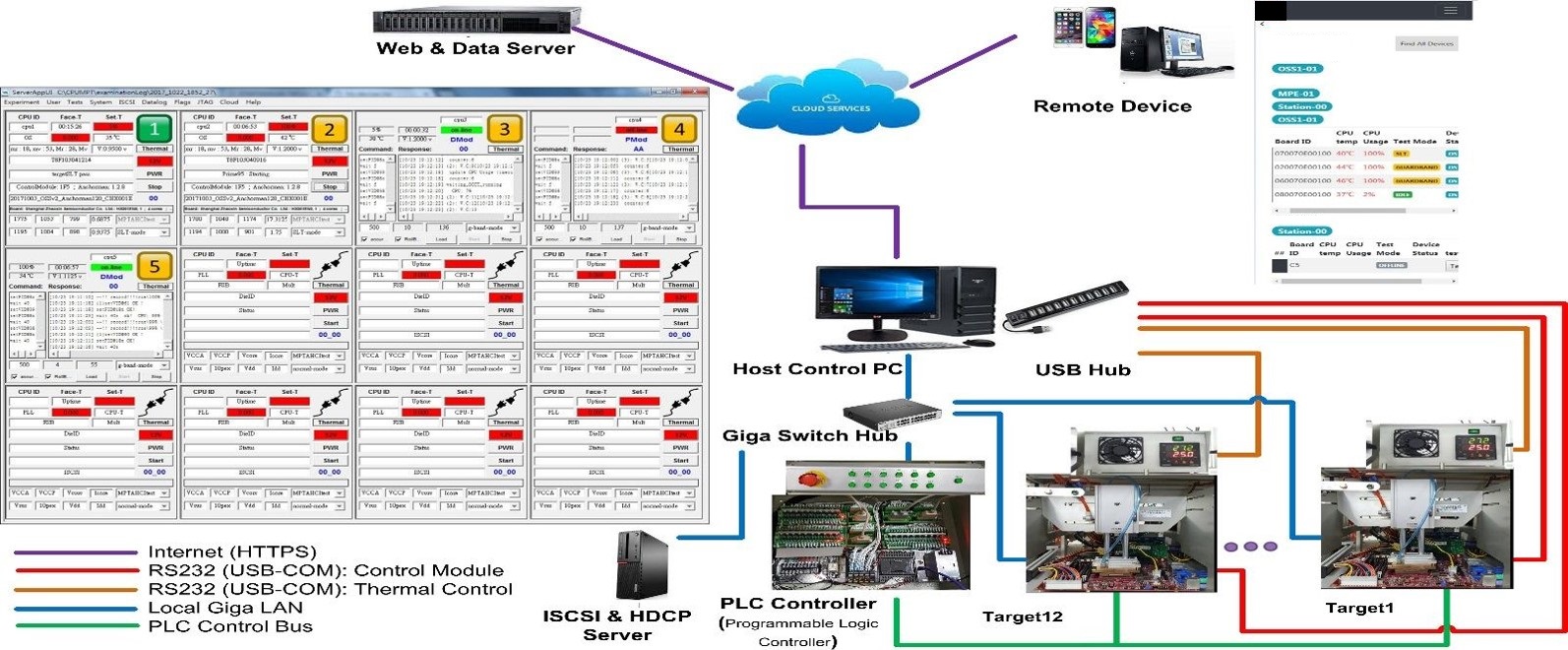

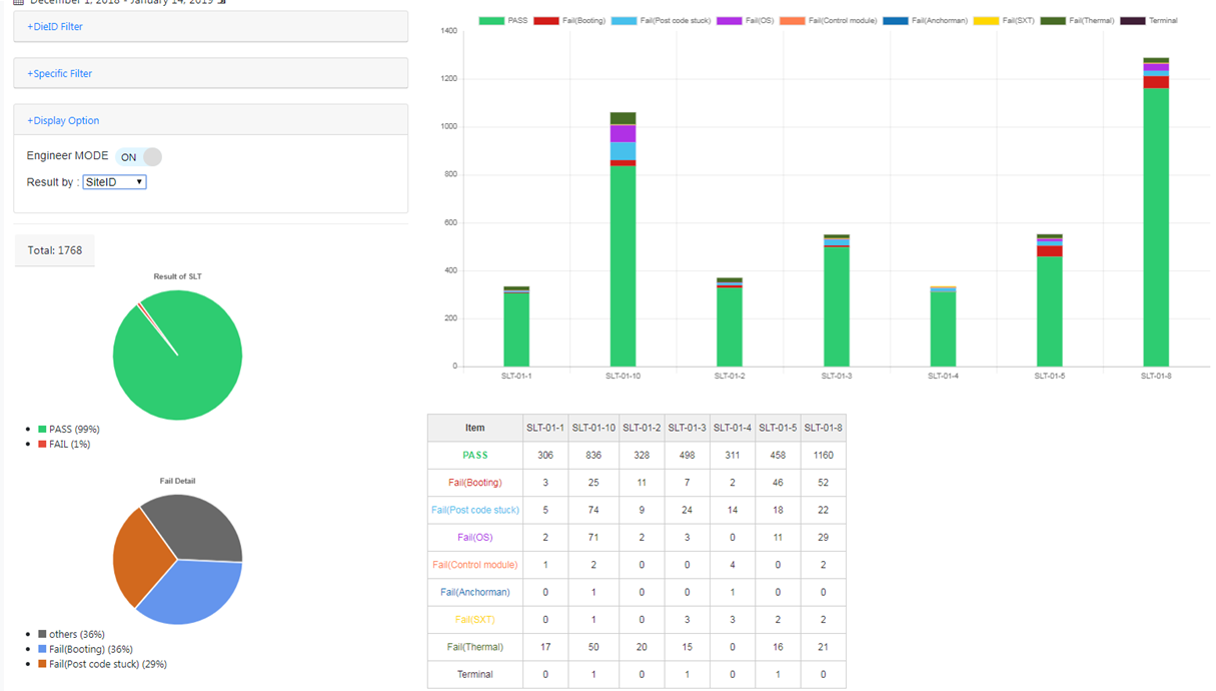

System Level Testing

VNCHIP uses advanced DFT and tailored solutions to streamline testing, optimize costs, and speed up product launch.

Warning: Attempt to read property "ID" on null in /var/www/html/wordpress/wp-content/plugins/elementor/includes/managers/image.php on line 113

Warning: Attempt to read property "post_excerpt" on null in /var/www/html/wordpress/wp-content/plugins/elementor/includes/managers/image.php on line 114

Warning: Attempt to read property "post_content" on null in /var/www/html/wordpress/wp-content/plugins/elementor/includes/managers/image.php on line 115

Warning: Attempt to read property "post_title" on null in /var/www/html/wordpress/wp-content/plugins/elementor/includes/managers/image.php on line 116

We provide:

- SLT Board and Thermal Control Design

- Customized SLT Software Development

- Real-Time Monitoring of Test Results and Platform Status

- SLT Data Collection and Analysis